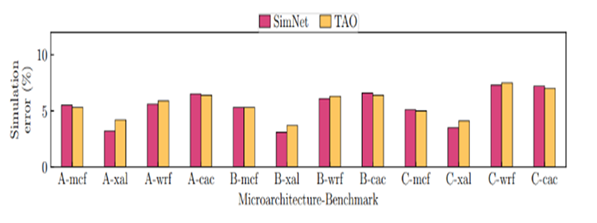

Simulation accuracy comparison with the state-of-the-art.

Invention Summary:

Microarchitecture designers rely on simulators to validate, optimize, and manufacture hardware that meets specific design requirements. Out of the current simulators, executive-driven simulators are often slow and require a high level of expertise, trace-driven simulators have low accuracy, and deep-learning-based stimulators fail to meet performance metrics such as causing branch mispredictions or cache misses.

Rutgers researchers have redesigned and optimized a deep-learning microarchitecture simulator, called Tao. By using a new training dataset design, researchers can rapidly generate and reuse these inputs across microarchitectures. Additionally, self-attention improved the detail of the simulator, and microarchitecture-agnostic embedding layers improved the speed of learning such that it significantly reduces the re-training overhead that would otherwise slow deep-learning based simulators. Tao has been shown to significantly reduce both the training and simulation time by 26.58x per microarchitecture design and maintain similar simulation accuracy as state-of-the-art DL-based endeavors.

Market Applications:

- Architecture design space exploration

- Microarchitecture bottleneck analysis

- Workload characterization

Advantages:

- Reduced training and simulation time

- Reusable functional trace inputs

- Predicts multiple performance metrics of interest

Intellectual Property & Development Status: Patent pending, provisional application filed. Available for licensing and/or research collaboration. For any business development and other collaborative partnerships contact: marketingbd@research.rutgers.edu